在最新的技术前沿探索中,三星电子的代表Song Jai-hyuk于IEEE ISSCC 2025全体会议上,对HBM内存的未来发展趋势进行了深入剖析。他提出了两项创新思路:一是通过定制版本减少I/O面积占用,二是在基础芯片中直接整合加速器单元。

关于定制HBM内存,Song指出,现有的HBM内存架构在xPU处理器与HBM基础裸片之间,依赖数以千计的PHY I/O进行连接。而定制版本则采用更为高效的D2D(裸片对裸片)互联技术。这一改进不仅缩短了芯片间的距离,还大幅减少了I/O数量,从而实现了更高的能效。D2D互联在面积占用上的优势,为xPU和Base Die提供了更多空间来集成先进的芯片IP。

值得注意的是,在定制HBM架构中,LPDDR控制器/PHY和HBM控制器从xPU芯片中移出,被整合到了HBM Base Die中。这一变动进一步简化了系统结构,提升了整体性能。

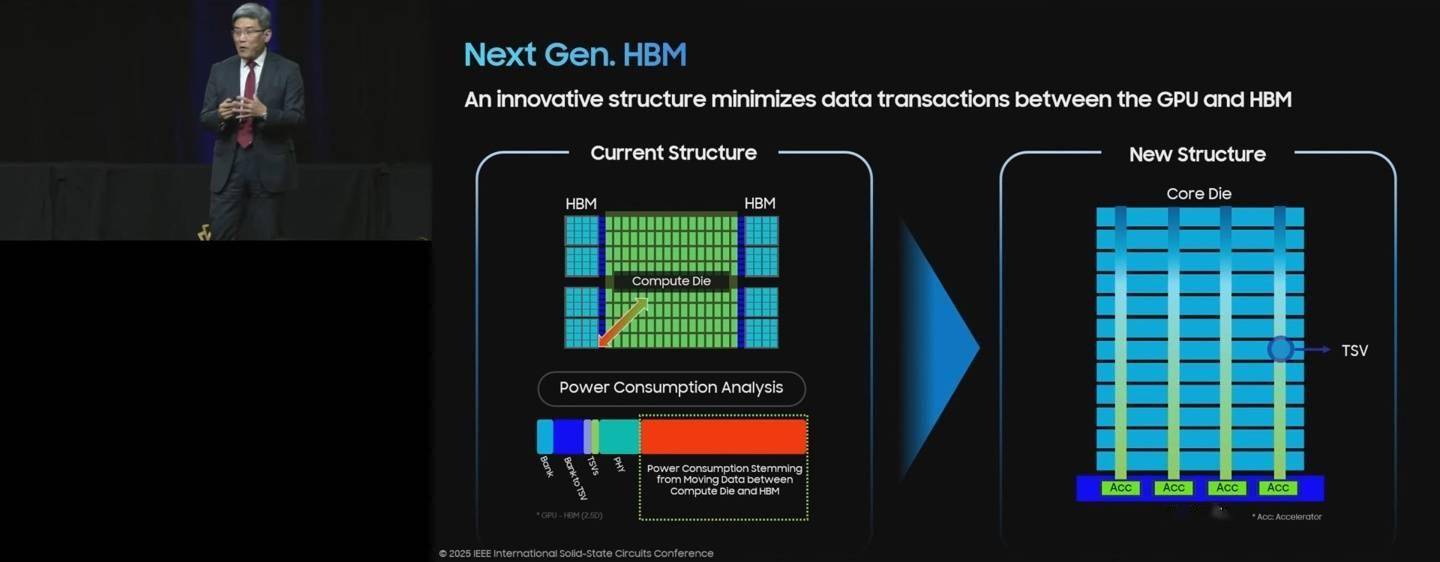

除了定制HBM内存外,Song还展望了3D集成HBM内存的未来。目前,HBM内存与处理器主要采用2.5D封装技术,但这一技术导致了大量功耗浪费在数据搬运过程中。为了克服这一局限,未来的HBM内存有望采用3D集成形式。

在3D集成HBM内存中,加速器单元将被直接内置于基础芯片中,并通过TSV(硅通孔)技术与DRAM芯片实现直连。这一设计彻底摒弃了复杂的中介层,极大地提高了数据传输的能效。这一创新不仅有望解决当前HBM内存面临的功耗问题,还将为未来的高性能计算领域开辟新的道路。